FPGA的时钟输入都有专用引脚,通过这些专用引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是...

”FPGA SDRAM 电路设计 时钟引脚连接 文章 单片机 FPGA“ 的搜索结果

本文是小编为广大读者搜罗来的关于FPGA时钟和复位电路的设计,供广大读者们参考学习。

本文介绍在FPGA设计中SDRAM电路的设计,对SDRAM的相关应用有很大的帮助。

所谓外部晶振方案,是指在单片机的时钟引脚X1与X2外部连接一个晶振 优点:时钟频率精度高,稳定性能好;对于一些数据处理能力要求较高的项目,尤其是多个电路系统彼此需要信息通讯,如包含USB通讯、CAN...

FPGA共有四种配置模式:从串模式(Slave Serial($566.8500)),主串模式(MasterSerial($566.8500)),从并模式(Slave Parallel/SelectMap)以及边界扫描模式(Boundary-Scan)。具体的配置模式由模式选择引脚M2...

8051单片机内核IP源码cyclone2 fpga quartu工程文件+文档说明, 可以做为你的FPGA设计学习参考。 该部分的8051内核的顶层信号引脚在8051内核的顶层便可查看到各个引脚模块的定 义。引脚的定义和普通的 8051 单片机...

野火征途Pro开发板FPGA数字时钟设计

管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。这一讲,我们将具体介绍

用always@(posedge clk)描述 时序逻辑电路的基础——计数器(在每个时钟的上升沿递增1) 例1.四位计数器(同步使能、异步复位) // Module Name: counter_4bit // Description: 4bit异步复位同步使能二进制计数器 ...

数字时钟设计2 本代码借鉴了一些,网上资源。 1.硬件资源:共阴极数码管一块,FPGA开发板一块(EP2C8Q208C8); 2.开发板资源:3颗独立按键,数码管接口; 3 功能设计:三种功能:a.时钟功能;b.校时功能;整点报时...

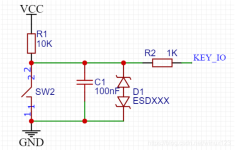

时钟硬件电路设计

SWD硬件电路设计

FPGA的引脚作用

在时钟信号驱动多个寄存器时,由于线网的传输延时...在默认情况下,驱动多寄存器的时钟在逻辑综合时,综合工具通常不会在时钟的连线上添加时钟缓冲器以提高驱动能力,而是将时钟输入端直接连接到所有寄存器的时钟引脚。

(1)准确计时,用数码管显示小时、分和秒;(2)小时以24小时计时;(3)带有时间校正功能;(4)“闹钟”功能;

以太网电路

引脚功能

推荐文章

- javafx预览PDF_javafx pdf-程序员宅基地

- ipv4与ipv6访问_纯ipv4访问纯ipv6-程序员宅基地

- css强制换行-程序员宅基地

- 链霉亲和素修饰的CdSe–ZnS量子点-程序员宅基地

- 饿了么4年 + 阿里2年:研发路上的一些总结与思考-程序员宅基地

- vue的sync语法糖的使用(组件父子传值)_sync传值-程序员宅基地

- 最大流最小割_网络最大流量与割的容量的关系-程序员宅基地

- queryString模块_querystring模块安装-程序员宅基地

- 安卓电量检测工具Battery Historian的使用记录_battery-historian 电量测试-程序员宅基地

- 基于QPSK的载波同步和定时同步性能仿真,包括Costas环的gardner环_qpsk符号同步-程序员宅基地